Schaltplan-Design für Hardware-Entwickler

Nach Eingang Ihrer Anmeldung erhalten Sie eine E-Mail mit den Zugangsdaten.

Webinar On-demand

Hardware-Entwickler beschäftigen sich in der Regel nicht permanent mit Schaltplan Designwerkzeugen. Abgesehen von Redesigns arbeiten sie pro Jahr an zwei bis drei Neuentwicklungen. Deshalb muss für sie das Werkzeug für die Schaltplanentwicklung leicht zu bedienen sein. Andererseits sollte der Schaltplaneditor auch in der Lage sein, Informationen für nachfolgende Arbeitsschritte zu transportieren, denn der Entwickler möchte nicht den gleichen Schaltplan für verschiedene Anwendungszwecke mehrfach in verschiedenen Schaltplan-Editoren erstellen.

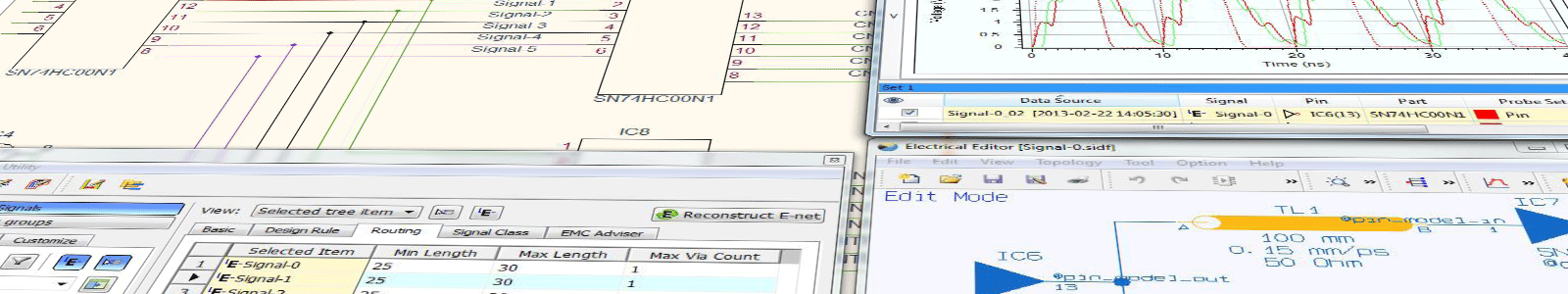

Typische Anwendungsfälle sind die Erstellung der Netzliste für das Leiterplatten-Design zur späteren Fertigung der Baugruppe. Die Vorgabe von elektrischen Regeln, den so genannten Constraint oder eben das simulieren von partiellen Schaltplänen mit einem SPICE-Simulator. In diesem Webinar wird gezeigt, wie auf der Basis von CR-8000 mit Hilfe einer modernen Engineering Plattform all diese Anwendungsfälle ohne das Erstellen von Kopien möglich ist.

Themen:

- Planung von Multi-Board Designs und Ableitung einer Gesamt-Netzliste

- Nutzung von Best-in-Class Simulationswerkzeugen für analog/mixed Signal, RF und System Level Analyse

- What-If Analysen zur Bestimmung von Terminierung und Topologie von kritischen Signalen

- Arbeiten mit Black-Box Symbolen und Bauteilen für entwicklungsbegleitende Implementierungsstudien.

Zielgruppe:

- Entwicklungsleiter

- Elektronikentwickler

- PCB Designer

Presenter: Martin Santen

Presenter: Martin Santen

Senior Application Engineer, Technical Competence Center Zuken GmbH, München.

Lorem ipsum dolor sit amet, consectetur adipisicing elit, sed do eiusmod tempor incididunt ut labore et dolore magna aliqua. Ut enim ad minim veniam.